Hace un par de semanas empezaron a salir rumores m�s precisos sobre las novedades que incluir� la arquitectura Zen 5 de AMD, una arquitectura que seg�n la compa��a est� dise�ada partiendo de cero "from the ground up" y por lo tanto con mejoras notables que deber�an hacerse notar.

En esa noticia aprendimos que el nombre en clave de Zen 5 es el de Nirvana y se destacaban varias mejoras principales como son la mejora de rendimiento y eficiencia, cambios en el pipeline del front-end y "wide issue", integraci�n de IA y optimizaciones en Machine Learning.

Ahora en WCCF Tech se hacen eco de lo que filtra AdoredTV, quien ya ha realizado varias filtraciones acerca de las arquitecturas de AMD y que ahora nos trae informaci�n acerca de las mejoras que recibir� Zen 5 en sus distintas memorias cach�.

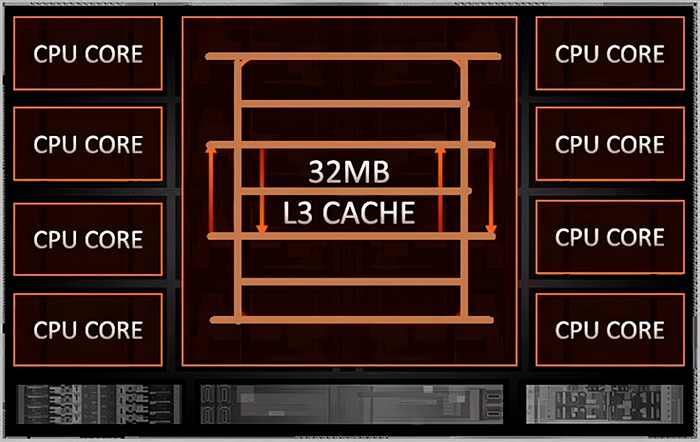

Aparentemente la cach� L3 sufrir� un importante cambio arquitect�nico, algo que no es nuevo dentro de la familia Ryzen y que en anteriores saltos se ha ido mejorando y eso se ha notado claramente. Nos comentan que inicialmente con la arquitectura Zen cada CCD contaba con hasta dos CCX de cuatro n�cleos, ah� cada CCX s�lo ten�a acceso a 16 MB de cach� del total de 32 MB de cach� L3 del CCD. Con la llegada de Zen 3 se reestructuraron los CCX para que tuviesen acceso a toda la cach� L3 del CCD, as� hasta 8 n�cleos pod�an compartir la misma cache en una conectividad tipo anillo.

Seg�n AdoredTV con Zen 5 se introducir� otra organizaci�n de la cach� en algo que bautizan como "Ladder" y que a�n no sabemos c�mo traducirlo en espa�ol puesto vendr�a a ser en forma de escalera. Esta nueva conectividad u organizaci�n de la cach� ayudar�a a reducir la latencia entre n�cleos que implicaba el dise�o en forma de anillo reduciendo as� los cuellos de botella que hay dentro de cada CCD.

Arriba vemos una imagen ilustrativa para entender el nuevo dise�o aunque ya mencionan que a�n no tienen clara la cantidad de cach� L3 por lo que debemos quedarnos con la idea.

Otro aspecto que se va a renovar es el de la cach� L2 y aqu� las cosas son m�s sencillas pero menos claras. Con Zen 1 hasta Zen 3 la cach� L2 por n�cleo era de 512 KB, con Zen 4 se aument� a 1 MB por n�cleo y con Zen 5 habr� otro aumento de cach� L2, como m�nimo se volver�a a duplicar pero podr�a llegar hasta los 3 MB.

Seg�n AdoredTV se est�n probando chips distintos con dos y tres MB de cach� L2 respectivamente, en la misma imagen vemos que 2 MB de cach� L2 implican un aumento de IPC alrededor del 4% en multihilo, mientras que con 3 MB el aumento de IPC subir�a hasta el 7%. En cambio en monohilo el aumento de cach� se notar�a muy poco y tendr�amos un incremento de apenas un 1%. Se se�ala que este aumento de cach� no implicar�a un aumento de latencias.

De la imagen de arriba no terminamos de entender esa suma que aparece entre las dos cantidades de cach� L2, y de hecho tampoco dan una explicaci�n de porqu� AMD est� probando chips de 2 y de 3 MB de cach� por lo que ah� se abre la puerta a la especulaci�n y podemos pensar que est�n buscando el punto �ptimo o, por otro lado podr�amos estar ante pruebas de n�cleos distintos como ser�a el caso de Zen 5 y Zen 5c, de hecho con Zen 4c se especula que la cantidad de cach� L2 sea mayor que con Zen 4 a cambio de reducir frecuencias.

Normalmente el tema de la cach� es algo que explica de forma transparente AMD cuando es el momento oportuno, as� que tarde o temprano sabremos la veracidad de estos rumores as� como las mejoras esperadas y los motivos concretos de estos ajustes.